| [이슈현장] SK-자일링스 FPGA 간담회 | |

| 2018-09-02 | |

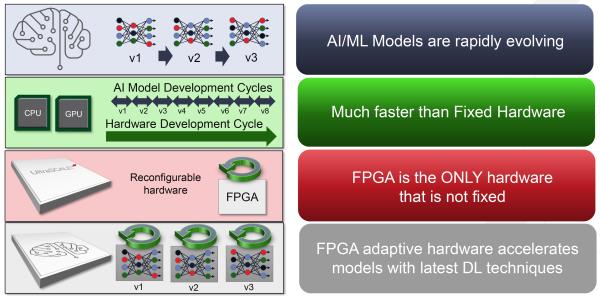

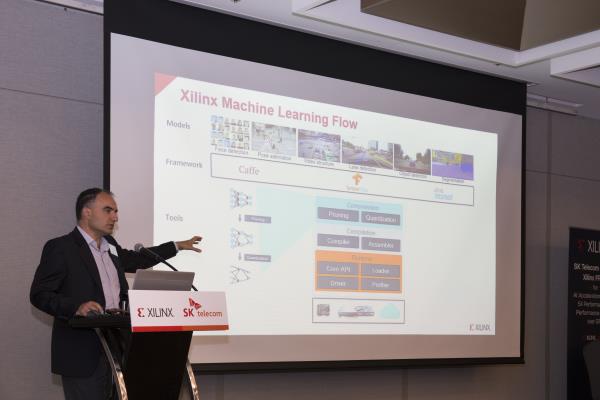

FPGA로 누구(NUGU) 서버 GPU 성능 5배 향상 전력소모·발열 낮추고, 공간절약까지 극대화해 SKT-자일링스 FPGA 기자간담회 그동안 AI 분야의 경우, 프로세싱은 더 잘하면서도 전력소모와 발열이 적은 새로운 네트워크 기술이 한 달에 한 번씩 새로 탄생할 정도로 개혁 속도가 빨랐다. 이에 비해 CPU나 GPU, ASIC(주문형 반도체)이 이러한 네트워크를 제대로 구현할 수 있을 정도로 효율적으로 지원하지 못해왔다. 하지만 최근에는 FPGA의 등장으로 이런 문제들이 하나둘씩 해결돼 가고 있다. SK텔레콤과 자일링스는 FPGA 개발에 관한 시의적절하게 파트너십을 구축해 AI 분야에서의 힘찬 도약을 준비하고 있다. 글·사진 김경한 기자 | 사진협조 자일링스 FPGA, 논리회로 재설정 가능 AI 및 딥러닝 분야에서 주목 SK텔레콤과 자일링스(Xilinx)는 지난 8월 16일 서울 강남구 그랜드인터콘티넨탈호텔에서 기자간담회를 열고, SK텔레콤의 데이터센터에 자일링스의 FPGA를 적용해 효율성을 높이는데 성공했다고 발표했다. 이 자리에서 SK텔레콤은 AI 음성인식 디바이스인 누구(NUGU)의 데이터센터에 자일링스의 FPGA를 적용함으로써 GPU 대비 5배의 성능향상을 실현하고 와트당 성능 면에서는 16배의 향상을 이뤘다고 밝혔다. FPGA(Field Progrmmable Gate Array)는 회로 변경이 불가능한 일반 반도체(주문형 반도체 등)와 달리 사용자가 수차례에 걸쳐 논리회로를 재설정할 수 있는 비메모리 반도체다. 최근 전자제품의 모델이 많아지고 교체주기가 짧아지면서 다품종 소량 적용에 적합한 FPGA의 활용도가 높아지고 있다. 자일링스 FPGA의 적응형 특성은 급속도로 진화하는 AI 및 딥러닝 분야에 맞춤형 하드웨어 가속기를 신속하게 배치하도록 할 수 있다. CPU 및 GPU에 비해 낮은 전력으로 더 높은 성능과 낮은 대기시간도 제공한다. SK텔레콤은 컴퓨팅 가속을 위해 FPGA를 배치한 유수의 상용 데이터센터 기업에 이름을 올리게 됐으며, 이런 기업들은 빠르게 증가하고 있다.  SKT, FPGA 95% 활용도로 최적화 성공 보안솔루션·자율주행 등 적용가능성 높아 이날 간담회에서 이강원 SK텔레콤 소프트웨어 기술원 원장은 자사 데이터센터에 자일링스의 FPGA를 적용한 이유를 적극적으로 설명했다. 이강원 원장은 “SK텔레콤의 AIX(AI 연산가속기)는 하이레벨 아키텍처이며, 자일링스의 FPGA로 가속화를 위한 최적화 모델을 구현했다”고 밝혔다. 그는 “자일링스의 FPGA를 서버에 장착하면, 서버 5대를 대체하는 효과가 있다”며 “발열이 적고 공간을 절약할 수 있다”고 강조했다.  SK텔레콤 기술진도 자체적으로 정적·동적 최적화를 위한 노력을 아끼지 않았다. 그 결과, 자일링스 FPGA의 DSP를 95% 이상 활용할 수 있었다. 통상적으로 DSP의 레인지가 60~70%인 것을 감안하면 SK텔레콤이 상당한 수준의 활용도를 갖춘 셈이다. 특히 한국에서 대규모의 데이터센터를 위해 AI 도메인에서 FPGA 가속기를 상용 채택한 것은 SK텔레콤이 최초의 사례로 꼽히고 있다. 이 원장은 “앞으로 누구(NUGU)의 데이터 용량이 커지더라도 데이터센터를 증설하지 않고 활용하는 것이 목표”라며 “향후 누구(NUGU)뿐만 아니라 ADT캡스의 보안솔루션 및 자율주행, 네비게이션 등에서도 자일링스와 협력해 좋은 파트너십을 유지해 나갈 것”이라고 말했다. 자일링스, FPGA 5배 이상 가속화 달성 구현환경 자동화로 개발 편의성 높여 라민 론(Ramine Roane) 자일링스 AI솔루션 마케팅 부사장은 자사 FPGA의 강점을 상세히 소개하며, SK텔레콤의 좋은 파트너십을 유지할 것임을 강조했다. 라민 론 부사장은 “자일링스의 FPGA는 기존의 GPU나 CPU와 비교했을 때 10배 이상 다양한 스케일로 가속화할 수 있다”고 밝혔다. 부연 설명으로 “GPU는 연동되는 분야가 머신러닝 등 적용되는 분야가 한정적이지만, 기존 CPU와 비교하면 10배의 가속화가 가능하다“고 주장했다. 이는 FPGA 카드 1개를 꽂은 CPU로 10개의 CPU를 대체할 수 있다는 의미다. 이 외에도 그는 바이오 IT 프로세서 개발업체인 Edico Genomics는 genomics(유전체학)에서 100배, 데이터분석 전문업체인 FYFT는 빅데이터 분석에서 90배의 클라우드 가속화를 실현했다고 밝혔다. 그래서인지 최근 데이터센터에서 기존 제품들을 FPGA로 교체하는 사례가 늘고 있다는 것이 라민 론 부사장의 설명이다.  자일링스의 공식자료에 따르면, FPGA 기반 가속기는 CPU 전용 서버에 효율적인 자일링스 FPGA 애드 인(Add-In) 카드를 추가해 ASR(자동음성인식, automatic speech recognition) 애플리케이션 서버의 총 소유 비용(TCO)를 낮출 수 있다. ASR 서버는 빈 슬롯에 자일링스 FPGA 카드를 사용해 쉽고 간단하게 여러 음성 서비스 채널을 가속화한다. 하나의 FPGA 카드는 단일 서버의 성능보다 5배 이상 뛰어나므로 상당한 비용절감 효과가 있다. 라민 론 부사장은 자일링스의 FPGA는 사용자 편의성을 제공한다는 말도 전했다. 그는 “보통 FPGA는 개발자 입장에서는 작업하기가 힘든 면이 있다”며 “하지만 자일링스는 자사 제품을 별다른 훈련이나 지식 없이도 구현할 수 있도록 자동화함으로써 (AI 가속기에) 바로 적용할 수 있도록 했다”고 밝혔다. 이어 그는 “SK텔레콤의 누구(NUGU)가 빠르게 성장 중”이라며 “포터블과 차량 안에 설치할 수 있는 제품이 개발되고 있기 때문에 앞으로 더욱더 크게 성장할 것”이라고 예측했다. 그러면서 “향후 양사는 음성인식뿐만 아니라 다른 분야에서도 협력을 지속해 나갈 것”이라고 덧붙였다. 자일링스는 전 세계 FPGA 시장의 60%를 점유하고 있다. 라민 론 부사장은 “데이터 시장이 2020년까지 260억 달러까지 성장할 것”이라며 “데이터센터에 사용되는 가속기 시장 규모도 끊임없이 늘어날 것이므로, FPGA도 더 많은 기업에서 수요가 있을 것으로 기대된다”고 전했다. * 한편 자일링스의 CEO는 과거 SK텔레콤을 방문한 적이 있다. 당시 그는 SK텔레콤이 자일링스 FPGA를 95% 활용한다는 사실을 듣고 적잖이 놀랐다고 한다. 그 덕분에 SK텔레콤은 향후 자일링스 관련 행사에서 FPGA 활용 관련 시연회를 진행하게 됐다. SK텔레콤의 FPGA 기반 AI 솔루션은 오는 10월 1~2일 미국 실리콘 밸리와 10월 16일 중국 베이징에서 개최되는 ‘자일링스 개발자포럼’에서 시연이 예정돼 있다.

< Energy News > |

|

- [전시회탐방/에너지현장] 분류 내의 이전기사

-

[이슈현장] AI 월드컵 2018

구글·MIT등12개국29개팀 출전한AI축구대회세계AI인재들이 함께하는 지식 및 기술 교류의 장AI월드컵2018KAIST가 지난8월20일부터22일까지 대전 본원 학술문화관(E9)정근모홀에서‘AI월드컵(AI World Cup

2018-09-02 -

[전시회탐방] 2018 국제그린카전시회

4차산업혁명 이끄는 차세대 자동차 기술 총망라글로벌업체 대거 참여 및6,618만 달러 수출상담 달성2018국제그린카전시회자동차업계에 따르면,친환경차의 글로벌 판매량이2020년에는800만 대를 돌파할 것으로 전망되

2018-08-04 -

[이슈현장]국내 최초 인공지능의 모든 것 한 자리에, 2018 국제인공지능대전

국내 최초 인공지능의 모든 것 한 자리에지적 호기심으로 눈과 귀가 즐거운 축제!2018 국제인공지능대전놀라운 자연어 인식 능력으로 퀴즈쇼에 출연해 센세이션을 일으킨 IBM 왓슨, 인간 바둑고수의 실력을 뛰어넘은

2018-08-04 -

세계의 동력이 될 한국의 우수 전력기자재, 대한민국의 꿈을 수출하다_2018 국제 전기전력 전시회

세계의 동력이 될 한국의 우수 전력기자재,대한민국의 꿈을 수출하다2018국제 전기전력 전시회한국전기기술인협회는 스마트그리드,발전·원자력 플랜트,중전기 산업을 융합한‘2018국제 전기전력 전시회(

2018-07-02 -

[이슈 현장]슈나이더 일렉트릭, ‘이노베이션 서밋 서울 2018’

슈나이더 일렉트릭, ‘이노베이션 서밋 서울 2018’‘이노베이션 허브’에서 최신 솔루션 선보여에너지 관리 및 자동화 분야의 디지털 혁신을 선도하는 글로벌 기업 슈나이더 일렉트릭(www.schn

2018-07-01

- 관련기사

-

[신제품] 키사이트, 5G 네트워크 에뮬레이션 솔루션 출시

키사이트, 5G네트워크 에뮬레이션 솔루션 출시2GHz대역폭 및 최대44GHz주파수 지원키사이트코리아(대표 최준호)가2GHz대역폭 및 최대44GHz주파수를 통합형 듀얼 채널로 지원하는 벡터 신호 발생기를 선보였다.이 제품

2019-05-01 -

[이슈현장] 5G 자율주행차 공개 시연

5G로 실시간 파악 후8km도심 자율주행끼어들기·차선변경·안전거리 확보도‘척척’5G자율주행차 공개 시연LG유플러스와 한양대학교 에이스랩(ACE Lab)은 지난3월11일 한양대학교 서울 캠퍼스

2019-04-01 -

[신제품] 키사이트, VXG 마이크로웨이브 신호 발생기 출시

키사이트, VXG마이크로웨이브 신호 발생기 출시듀얼 채널44GHz주파수 및2GHz대역폭 지원키사이트테크놀로지스가 하나의 계측기에서 최대44GHz주파수 및2GHz변조 대역폭의 신호를 듀얼 채널로 지원하는VXG마이크로웨이

2019-04-01 -

[신기술] 생명체의 우수성을 모방하는 디지털 기술

생명체의 우수성을 모방하는 디지털 기술반도체 소자 및 연료전지 성능향상에 활용NASA(미국항공우주국)가 화성으로 보낸 탐사로봇 큐리오시티는 거미의 팔다리를 닮은 로봇팔과 바퀴다리를 지니고 있으며,지진 시 수

2019-02-01 -

[신기술] 반도체 호황기 이어갈 제조공정 기술

반도체 호황기 이어갈 제조공정 기술공정 단순화와 자유도 향상으로 효율성 극대화국내 반도체 업계가 올해3/4분기에 사상 최대 실적을 기록했다.삼성전자는 이 기간에 반도체사업에서만 매출65조4천600억 원,영업이

2018-12-01